# **Squash Reuse via a Simplified Implementation of Register Integration**

**Amir Roth**

Department of Computer and Information Science University of Pennsylvania 200 S. 33rd Street Philadelphia, PA 19104

#### Gurindar S. Sohi

Computer Sciences Department University of Wisconsin-Madison 1210 W. Dayton Street Madison, WI 53706 AMIR@CIS.UPENN.EDU

SOHI@CS.WISC.EDU

#### Abstract

Register integration (or simply integration) is a mechanism for the direct reuse of previously computed results. Integration uses data-dependence relationships to test for and establish reusability. In this paper, we use integration to implement squash reuse, the salvaging of instruction results that were needlessly discarded during the course of sequential recovery from a control- or data- mis-speculation.

In integration, the results of squashed instructions remain in the physical register file past mis-speculation recovery. As the processor re-traces portions of the squashed path, an auxiliary table is used to search the physical register file for the registers belonging to the corresponding squashed instances of re-traced instructions. If found, a squashed register is re-validated by a simple update of the rename table. The integrating re-traced instruction completes instantly and bypasses the out-of-order core. Integration reduces contention for execution resources, collapses dependent chains of operations and accelerates branch resolution. It achieves this using only rename-table manipulations; without reading or writing the physical registers themselves.

We present a simplified implementation of register integration that uses explicit states to manage physical registers and in-order pre-retirement re-execution (much simpler than general out-of-order execution) to guarantee integration correctness. We also introduce a simple mechanism that learns from past integration mistakes to avoid similar mistakes in the future. These components contribute to a design that is simple, high-performing, easy to pipeline, and which has minimal impact on the rest of the microarchitecture.

Our preliminary evaluation shows that a minimal integration configuration can provide performance improvements of up to 5% when applied to next-generation microarchitectures. Integration also reduces the amount of wasteful speculation in the machine, cutting the number of instructions executed by up to 17% and the number of instructions fetched along mis-speculated paths by as much as 6%.

### **1** Introduction

Modern microprocessors rely heavily on *speculative execution*. Sequential processors (ones that execute sequential programs) speculate on both control and data, executing instructions before all of their input dependences are known with certainty. Successful speculation improves performance by sparing the speculated instructions the delay of execution context verification. On the other hand, unsuccessful speculation, or *mis-speculation*, hurts performance by forcing the processor to *recover* to some prior non-speculative state and start over. This paper presents *register integration*, a mechanism for overcoming an inherent inefficiency in conventional sequential mis-speculation recovery.

The inefficiency in question is the result of a basic antagonistic combination found in sequential programs. While a sequential program is composed of many *locally independent computations*, the *state* of the program is only defined sequentially at dynamic instruction boundaries. Since mis-speculation recovery is defined in terms of this sequential state, a mis-speculation in one computation inadvertently but necessarily causes valid work from sequentially younger computations to be aborted, or *squashed*, and re-executed. Register integration can perform *squash reuse* [3, 19, 21], salvaging the results of squashed computations that are control- and data- independent of the particular mis-speculation event that led to their squashing.

Many processors implement speculation using a level of indirection that maps the architectural register name space to a larger physical register storage space. The larger physical space allows multiple versions of each architectural location (all but one of which is speculative) to simultaneously exist. Successful speculation involves the promotion of newer mappings to non-speculative status. Mis-speculation recovery restores prior mappings and recycles the speculative storage. Integration is motivated by the observation that only restoration of previous mappings is required for correct recovery. If the speculative values are left intact past a recovery event, then should the processor re-trace part of the squashed path and discover that some of the instructions were useful after all, only the corresponding mappings will need to be restored; the values themselves will already exist and will not need to be re-computed.

The matching of squashed results with re-traced instructions is accomplished using a second mapping into the physical register file, the *Integration Table (IT)*. The IT differs from the sequential mapping (*map table*) in a fundamental way. The map table describes the contents of the physical registers in a transient, sequentially-dependent way from the point of view of the architectural registers. In contrast, the IT describes the contents of the physical register file operations and dataflow relationships used to create the values. As an instruction is register-renamed, the IT is used to search the physical register file for a physical register that holds the result of a previous squashed instance of the same instruction. If a register is found such that its creating instruction instance had the same physical register inputs as the currently renamed instance, then the currently-renamed instruction is "recognized" as having been previously executed and squashed. The current instruction *integrates* the squashed result by setting the sequential mapping for its output to point to the physical register allocated during the initial (squashed) execution. The *integrating instruction* is complete for all intents and purposes; it can commit as soon as the retirement algorithm allows.

Integration has several advantages. It reduces consumption of and contention for execution resources. It also collapses data-dependent chains of instructions: a chain of data-dependent instructions cannot be executed in a single cycle, but a completed chain of data-dependent instructions may be integrated in a single cycle. Integrating branch instructions are resolved immediately, and should these be mispredicted branches the misprediction penalty and subsequent demand on the fetch engine are also reduced. From an engineering standpoint, integration is simple to implement. It requires no additional data paths to either read or write physical register values and in general involves modifications only to the register renaming and retirement stages; the rest of the pipeline is oblivious to its existence.

Our experiments show that a realistic integration configuration can achieve speedups of up to 6% on a representative next-generation microarchitecture. Integration also reduces the level of wasteful speculation in a processor, cutting the number of instructions fetched along mis-speculated paths by as much as 6% and the number of instructions executed by 17%.

We initially conceived of register integration as a mechanism for allowing a master thread to directly use results pre-executed on its behalf by "helper" threads [18, 20]. The squash reuse application became evident during the initial simulator implementation. Since that first exposition, we have gained much experience with integration—in both squash and pre-execution reuse capacities—and have simplified and improved its (simulated) implementation in several ways. The implementation presented here represents the cumulative sum of our experience and is, in many places, quite different than its predecessor design.

The rest of the paper is organized as follows. The next section presents the basic integration algorithm and argues for its correctness. Section 3 addresses implementation issues. In section 4 we evaluate integration using cycle-level simulation. Section 5 discusses related work. Section 6 presents our conclusions.

### 2 Register Integration

During the course of processing, the program's dataflow graph, in the form of the results of its individual instructions, is stored in the physical register file. At any point in the program, the "active" vertices (results) of this graph are available through a set of mappings that maps architectural register names to

physical register locations and their values. New portions of the dataflow graph can only be attached to these "active" vertices. As each instruction is added to the graph, a physical register to hold its value is allocated and mapped to the architectural output. Each instruction is annotated with both the physical register holding its value and the prior physical register mapping of the same architectural location. Recovery entails backtracking over a portion of the program, restoring the previous mapping of each instruction's output while recycling the storage for the squashed result.

Integration exploits the observation that mis-speculation recovery is obligated only to restore some prior sequential mapping into the physical register file. That the results associated with the discarded mappings are also recycled during recovery is only an implementation convenience; leaving them intact past the mis-speculation does not impact correctness (of course, they must be recycled eventually lest the processor "leak" away all physical registers). Assuming the results are kept, let us consider the point immediately after the completion of a recovery sequence. Just at this point, all squashed instructions are, in principle, still "attached" to the current state (dependence graph) of the program as defined by the register mapping. The inputs of the oldest squashed instructions are found in this mapping. The fact that the inputs are valid validates the outputs, which are themselves inputs of younger squashed instructions, and so on. Integration is the process of transitively recognizing this validity, instruction by instruction.

For every instruction renamed by the processor, integration logic looks for a physical register associated with a squashed instance of that instruction and in particular, a squashed instance that executed with the same physical register inputs as the current instance is about to use. To facilitate this search, integration relies on the *Integration Table (IT)*, an auxiliary structure that indexes and tags physical registers using the PC—which represents the opcode and any immediate inputs in the instruction—and input physical registers of the creating instructions. If a physical register matching this description is found in the IT, we "unsquash" it by simply attaching it to the current instruction and re-entering it into the sequential map table. Attaching a squashed physical register to an active instruction implements reuse. Entering the physical register into the map table re-validates the input mappings of squashed results that depend on it, allowing them to be subsequently integrated. This same mechanism naturally avoids the reuse of results whose data inputs have been invalidated. As the processor sequences instructions from paths different than the squashed one, the results of these instructions create mappings to new physical registers not found in the squashed dataflow graph. These new mappings effectively "detach" those portions of the squashed dataflow graph that depend on the corresponding architectural name, preventing them from being integrated.

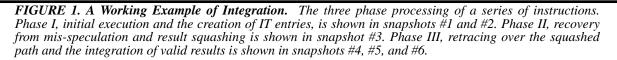

An example will hopefully clarify this process. Figure 1 shows six execution snapshots of a short program fragment that uses two register variables: r1 and r2. Each snapshot shows the program after the renaming of the last instruction, which is in bold. Each instruction is shown both in raw (logical register) and renamed (physical register) forms. To the right of the program is the state of the register map table. The register map table is not really shown in snapshot form, rather each line in the map table corresponds to its state after the renaming of the corresponding instruction on its left. The current state of the map table is simply the last entry. Finally, on the right of each snapshot is the current state of the IT. For this example, we use a 6-entry fully associative IT in which we create and evict entries in circular fashion. Each IT entry contains four fields: PC is the PC of the corresponding instruction instance, I1 is the input physical register, O is the output physical register (the one indexed by the entry and which we hope to integrate), and S is the state of that register. Each physical register can be in one of two states: *active* (A) or *squashed* (S). We use a single input physical register per entry to allow the figure to fit on a single page and because each instruction in our example has a single register input. A real IT would have two input register fields, I1 and I2.

The program undergoes three processing phases. In the first phase (snapshots #1 and #2), instructions A1 through A7 are renamed and executed. For each new instruction, a new physical register is allocated to hold its output value and an IT entry is created indexing this physical register. For instance, in snapshot #1, an IT entry is created for instruction A4. The output physical register is the newly allocated p2 (markers #1a). The input physical register is p0, the previous mapping of r1 (markers #1b). IT entries are created in the "active" (A) state indicating that the current entry refers to an in-flight instruction. The second phase takes place after all the instructions have completed execution, when a branch misprediction is detected at

instruction A3 (snapshot #3). At this point, instructions A4 through A7 are squashed and the map table is recovered to its post A3 state. In addition, as part of this process, we also transition the IT entries corresponding to the squashed instructions to the "squashed" (S) state. Integration comes into play in the final phase. Having recovered from the misprediction, the processor resumes fetching at the reconvergent point beginning at A5. We follow the renaming and potential integration of each instruction.

Intuitively, the retraced instance of A5 should be integrated since removing A4 did not change the value of r2. Indeed, when A5 is renamed for a second time (snapshot #4) r2 is mapped to p1, the same mapping it had during A5's original, squashed execution. Properly, the IT contains an entry for an instance of A5 with input physical register p1. By comparing PC/input-register tuples from the dynamic instruction and map table with the corresponding IT tuples (markers #4a), we determine that integration can take place. The act itself consists of setting the output mapping of A5 to the physical register originally allocated for it, p3 (marker #4b). p3 is also entered as the current mapping of r2 in the map table (marker #4c). The IT entry is returned to the "active" (A) state to prevent the physical register from being integrated by another instruction (marker #4d).

In contrast with A5, the retraced instance of A6 should *not* be integrated. The original squashed instance read a value written by A4. However, A4 was squashed and not retraced meaning the old value of A6 is

| -                                      |              |                       |                                 |              |            |

|----------------------------------------|--------------|-----------------------|---------------------------------|--------------|------------|

| <b>9</b><br>Dynamic Instruction Stream | Мар          | IT                    | 2<br>Dynamic Instruction Stream | Мар          | IT         |

| PC instruction renamed                 | r1 r2        | PC I1 O S             | PC instruction renamed          | r1 r2        | PC I1 O S  |

| A1 add r1,r0,#0 add p0,-               | p0 p7        | A1 - p0 A             | A1 add r1,r0,#0 add p0,-        | p0 p7        | A7 p3 p5 A |

| A2 add r2,r0,#1 add p1,-               | p0 p1        | A2 - p1 A             | A2 add r2,r0,#1 add p1,-        | p0 p1        | A2 - p1 A  |

| A3 beqz r1, A5 beqz -,p0 1             | b p0 p1      | A3 p0 - A             | A3 beqz r1, A5 beqz -,p0        | p0 p1        | A3 p0 - A  |

| A4 add r1,r1,#1 add p2,p0              | <b>p2</b> p1 | A4 p0 p2 A            | A4 add r1,r1,#1 add p2,p0       | p2 p1        | A4 p0 p2 A |

| 1a                                     | 1a           | <b>1</b> b <b>1</b> a | A5 add r2,r2,#2 add p3,p1       | p2 p3        | A5 p1 p3 A |

| _                                      | •            |                       | A6 add r1,r1,#3 add p4,p2       | p4 p3        | A6 p2 p4 A |

|                                        |              |                       | A7 add r2,r2,#4 add p5,p3       | p4 <b>p5</b> |            |

|                                        |              |                       |                                 |              |            |

| 3                                      |              |                       | 4                               |              |            |

| Dynamic Instruction Stream             | Мар          | IT                    | Dynamic Instruction Stream      | Мар          | IT         |

| PC instruction renamed                 | r1 r2        | PC I1 O S             | PC instruction renamed          | r1 r2        | PC I1 O S  |

| A1 add r1,r0,#0 add p0,-               | p0 p7        | A7 p3 p5 <b>S</b>     | A1 add r1,r0,#0 add p0,-        | p0 p7        | A7 p3 p5 S |

| A2 add r2,r0,#1 add p1,-               | p0 p1        | A8 p4 p6 <b>S</b>     | A2 add r2,r0,#1 add p1,-        | p0 p1        | A8 p4 p6 S |

| A3 beqz r1, A5 beqz -,p0               | p0 p1        | A3 p0 - A             | A3 beqz r1, A5 beqz -,p0        | p0 p1 4a     |            |

|                                        |              | A4 p0 p2 <b>S</b>     | A5 add r2,r2,#2 add p3,p1       | p0 <b>p3</b> | A4 4a p2 S |

|                                        |              | A5 p1 p3 <b>S</b>     | 4b                              | 4c           | A5 p1 p3 A |

|                                        |              | A6 p2 p4 <b>S</b>     |                                 |              | A6 p2 p4 S |

|                                        |              |                       |                                 |              |            |

| 5                                      |              |                       | 6                               |              |            |

| Dynamic Instruction Stream             | Мар          | IT                    | Dynamic Instruction Stream      | Мар          | IT         |

| PC instruction renamed                 | r1 r2        | PC I1 O S             | PC instruction renamed          | r1 r2        | PC I1 O S  |

| A1 add r1,r0,#0 add p0,-               | p0 p7        | A7 p3 p5 S            | A1 add r1,r0,#0 add p0,-        | p0 p7        | A7 p3 p5 A |

| A2 add r2,r0,#1 add p1,-               | p0 p1        | A8 p4 p6 S            | A2 add r2,r0,#1 add p1,-        | p0 p1        | A8 p4 p6 S |

| A3 beqz r1, A5 beqz -,p0               | p0 p1        | A6 p0 p9 A            | A3 beqz r1, A5 beqz -,p0        | p0 p1        | A6 p0 p9 A |

| A5 add r2,r2,#2 add p3,p1              | p0 p3        | A50p0 p2 S            | A5 add r2,r2,#2 add p3,p1       | p0 p3        | A4 p0 p2 S |

| A6 add r1,r1,#3 add p9,p0              | <b>p9</b> p3 | A5 p1 p3 A            | A6 add r1,r1,#3 add p9,p0       | p9 p3        | A5 p1 p3 A |

|                                        |              | A6 p2 p4 S            | A7 add r2,r2,#4 add p5,p3       | p9 <b>p5</b> | A6 p2 p4 S |

invalid in this new context. This invalidation is naturally captured by the IT. When A6 is renamed for the second time (snapshot #5), it finds its input r1 mapped to physical register p0. However, no entry for A6 with an input of p0 is found in the IT. The A6 entry has p2 (the register allocated by A4) as its input (marker #5a). Since integration is impossible in this case, a new physical register, p9, is allocated to the current instance of A6, and a new IT entry is created for this instance (marker #5b). The old entry for A6 (marker #5a) will remain in the IT until it is evicted.

Recall, when we integrated A5, we entered the integrated output (p3) into the map table. That action set the stage for the integration of A7, an instruction that depends on A5. The squashed version of A7 was executed with input register p3, the output of the squashed A5. When A7 is retraced (snapshot #6), its input is again p3 thanks to the integration of A5. A7 integrates p5 in exactly the same manner that A5 integrated p3.

In a superscalar processor, the integration decision on these instructions can be made in parallel. How this is done is the subject of the next section. However, the example demonstrated the three basic cases for superscalar integration: basic integration (A5), basic non-integration (A6), and the integration of an instruction that depends on an integrating instruction (A7).

### **3** Implementation

We now discuss the implementation of integration-based squash reuse by describing the necessary modifications to a representative base microarchitecture. An integration implementation comprises three components: 1) the *integration engine*, 2) the *integration application manager*, and 3) the *integration verifier*.

The *integration engine* is the heart of register integration. It consists of the physical register representation that fundamentally enables integration and the logic that implements the integration operation as a part of register renaming. Modulo some fine details, there is a *canonical* implementation of the integration engine which follows directly from the basic definition of the integration operation itself.

The *integration application manager* is responsible for managing physical registers in a way that fits the application. The application manager implements the policies that govern which physical registers become integration-eligible and when and how this transition takes place, what happens to integrating instructions, and how un-integrated physical registers are eventually recycled back to the free list. Per its name, the implementation of this component depends on the particular integration application. Squash reuse requires a different set of policies than pre-execution reuse. However, even for a given application there are many possible register management policies and many implementations of these policies.

The primary function of the *integration verifier* is to deal with *mis-integrations*, or incorrect integrations. The primary mis-integration scenario involves loads. An integrating instruction can be thought of as having two executions: a *physical execution* where the instruction is actually executed and then squashed, and an *architectural execution* in which the integrating instruction is supposed to execute but doesn't actually do so. For instructions with only register inputs, integration is perfectly safe. A valid combination of operation and input values (denoted by PC and physical registers) guarantees that the result of the physical execution is identical to that which would be produced in the architectural execution, allowing the former to be substituted for the latter. Loads are the exception. Older stores act as implicit inputs (via memory) to loads. Being purely a register discipline, register integration cannot track these dependences. The integration of a particular load is not guaranteed to be safe. A conflicting store may exist along the architectural execution path that was not present in the physical execution path, or vice versa. The integration of a load in the presence of such store differences between its physical and architectural paths produces an incorrect execution, which we call a *mis-integration*. A second, much rarer mis-integration scenario arises from the presence of stale IT entries (discussed in Section 3.4.1). It is the job of the integration verifier to detect mis-integrations, and prevent the corresponding instructions from retiring.

Like the application manager, the verifier is not fundamentally tied to the integration operation itself. Several verifier implementations are possible. The verifier may avoid mis-integrations *a priori* by tracking

## ROTH & SOHI

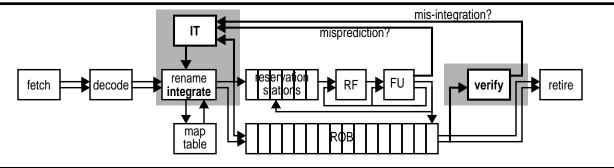

FIGURE 2. Pipeline with Register Integration. Integration specific structures and paths are in bold.

writes to addresses of integration eligible loads [19, 21]. Alternatively, a verifier implementation may allow mis-integrations to take place, detect them post fact via re-execution, and reverse them in some way. The division of labor between the application manager and the integration verifier is somewhat flexible. One instance of this fluidity is the handling of stale IT entries. We can implement a register management policy that will recursively invalidate and reclaim IT entries when they become stale. Alternatively, we can permit the integration of stale physical registers, and allow the verifier to catch the resulting mis-integrations. The implementation of verification is discussed in greater detail in section 3.4.

Figure 2 shows a dynamically scheduled, superscalar pipeline modified to include register integration. We will refer to this figure for the rest of this section. The additions and modifications required to support register integration in general and squash reuse in particular are shown in bold. The integration engine is centered around the register renaming stage and includes the integration table (IT) and integration circuit (added to register renaming logic). The integration verifier is inserted immediately prior to the retirement stage. The integration application manager is not explicitly shown, it is embodied in a set of rules and policies that use the other two components to implement squash reuse.

### **3.1 Base Microarchitecture**

In its current formulation, integration is not implementable in all microarchitectures. Integration requires that the base microarchitecture allow speculative results to remain intact past a mis-speculation recovery action and that it support the out-of-order allocation and freeing of speculative storage. These requirements disqualify many microarchitectures. In-order speculative microarchitectures like Sun's UltraSparc-III that use working (future) register files indexed by architectural register number both disallow arbitrary assignments of physical results to architectural names and overwrite the mis-speculated instructions' results during recovery. Intel's P6 [9] processor and HAL's SPARC64 V [6] keep speculative results in the reorder buffer, preventing their preservation past a mis-speculation recovery. IBM's POWER3 [22] processors and AMD's K7 [5] have physical register files separate from the reorder buffer, but also have an architectural register file and require that physical registers be allocated and freed in-order. Microarchitectures with physical register models that *can* support integration are the out-of-order Alpha processors starting with the 21264 [11], those of MIPS beginning with the R10000 [24], and Intel's Pentium 4 (the NetBurst microarchitecture) [8].

# 3.2 Integration Application Manager: Squash Reuse

In this section, we describe the squash-reuse application of register integration by explaining the modified handling of correct-path (i.e., eventually retired), squashed, and integrating (i.e., squash-reused) instructions. Our reuse management uses *explicit physical register states*.

# 3.2.1 Application Management Using Register States

An effective implementation of squash reuse demands that, at any point in time, results belonging to the most recent squashed instructions reside in the IT. To accomplish this, we initially proposed a scheme that

treated the IT as a holding station for squashed results on their (logical) way from the reorder buffer to the free list [19]. We saw this scheme as "evolutionary" because it required no changes to the semantics or handling of the two existing structures: the reorder buffer and free list. The effect of a third physical register state—that of a "squashed" physical register waiting to be integrated—was achieved implicitly. Register state was inferred based on presence in or absence from the IT. In our ensuing research, we have found that such a scheme has three important disadvantages. First, it is not sufficient in cases when multiple applications of integration—for instance squash reuse and pre-execution reuse—are implemented simultaneously. We ignore this problem for now, as squash reuse is the only application that interests us here. Second, it compresses the creation of IT entries into bursts which the IT may not be engineered to handle. Third and most importantly, it forces the IT into the dual role of integration broker and register manager, an antagonistic combination that results in sub-optimal operation on both fronts. Due to these disadvantages, we now prefer a management scheme based on explicit register states.

Creating IT entries during mis-speculation recovery is acceptable if recovery is performed serially. However, in most microarchitectures, including the Alpha 21264 [11] and MIPS R10000 [24], recovery is implemented as single-cycle restoration from a checkpoint. To avoid slowing the recovery process by burdening it with the creation of large numbers of IT entries, we adopt the approach of creating IT entries for *all* instructions during register renaming and only performing bulk changes to *register state* during recovery. This approach demands that we allow entries for physical registers in all states to reside in the IT. This, in turn, requires that we represent register states explicitly because presence in the IT no longer distinguishes integration-eligible "squashed" registers from integration-ineligible "active" or "free" registers.

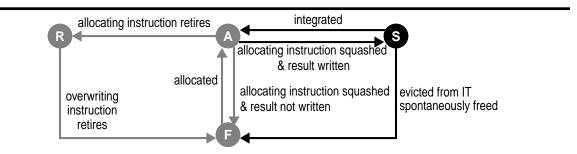

Our register state model is shown in Figure 3 at the bottom of this page. It includes the three register states that are implicitly used in a conventional superscalar processor and the transitions among them. These states are F(ree), A(ctive), and R(etired). Free registers are not associated with any value and are recognized by their presence in the free list. Active registers are associated with the speculative results of inflight instructions and are recognized by corresponding entries in the reorder buffer. Retired registers correspond to the last known architectural values of the logical registers and are recognized by their absence from both the free list and the reorder buffer. The transitions between these states occur during renaming (free to active), retirement (active to retired, retired to free), and mis-speculation recovery (active to free).

To implement squash reuse, we add a fourth state and three transitions. Rather than transition to the Free state on mis-speculation recovery, the destination registers of squashed instructions transition to the S(quashed) state where they await integration. If a Squashed register is successfully integrated, it transitions back to the Active state. Notice, according to this model, a register may transition back and forth between the Active and Squashed states multiple times. This corresponds to the undesirable but perfectly natural case of an instruction being squashed (and integrated) multiple times due to independent mis-speculation events. If a Squashed register is not integrated, it eventually transitions back to the Free state. Here, "eventually" corresponds to the need for a free register by a running thread, eviction from the IT, or the overwriting of an input register mapping. The problem of "leaking" Squashed registers is disposed of in a trivial way. It is always correct to transition a Squashed register to the Free state. Such a transition only prevents a subsequent integration opportunity and does not constitute incorrect execution.

FIGURE 3. Physical Register States and Transitions for Register Integration-Based Squash Reuse. The state and transitions used to implement squash-reuse are in black.

In the Figure 1 example, we showed state as represented in the IT itself. This may be the actual implementation, or it may be that states are represented in a separate vector that maps physical register number to state bits. Such a vector then performs double duty as the free list. We prefer the vector implementation since it allows bulk transitions to be performed using vector operations rather than IT accesses.

### 3.2.2 Handling Squashed Results and Integrating Instructions

Integration requires that we create IT entries for renamed instructions. This is not a strict requirement as failure to create an IT entry only implies forfeiture of future integration should the corresponding instruction be squashed *and* retraced. Be that as it may, IT creation applies to all instructions, squashed or not.

Integration also requires modifications to the recovery process. Recall, it is during this process that we perform bulk state transitions on the physical register state vector. In a conventional processor, one can think of the recovery procedure as simple replacement of the current state vector with some checkpointed version. In an implementation of integration-based squash reuse, one may think of the squash procedure as performing the following state vector operation: the current vector is replaced with a checkpointed version except that all physical registers that are in the Active state in the current version and the Free state in the checkpointed version are transitioned to the Squashed state. In other words, all registers that have been "activated" (allocated) since the checkpoint are "squashed". This conceptually simple operation is correct, but can be refined to improve IT performance and to simplify the handling of integrating instructions. The specific refinement we refer to is that we would like to transition to the Squashed states only physical registers that have already been written, i.e., whose corresponding instructions have completed execution. The reason is that it is the integration of *completed* results that contributes most to performance. Integration provides two main performance benefits: 1) it allows instructions to bypass the out-of-order execution engine and 2) it collapses dependent chains of instructions. Neither of these benefits applies to instructions that have not issued and only the first applies to instructions that have issued but not completed. However, the number of results likely to be integrated in this post-issue/pre-completion state is small. In return for forfeiting them, we simplify the handling of integrating instructions by treating them all as complete.

Allowing only written results to be integrated greatly simplifies the handling of integrating instructions. An integrating instruction is entered into the reorder buffer and marked as complete. Each entry in the reorder buffer is extended with a *integrating bit* which is set for all integrating instructions. Integrating loads (and stores) are allocated load (or store) queue entries that are also marked as complete. If the integrating instruction is a branch, its resolution and any potential recovery sequences are started immediately. In general, an integrating instruction bypasses the out-of-order execution core entirely; it is not allocated to a reservation station, scheduled, executed, or written back. Integrating *stores* are re-issued to the store queue to allow their values to be forwarded to subsequent loads via the conventional store queue channel.

### 3.3 Integration Engine

At the center of the integration mechanism is the integration circuit itself. The integration circuit examines each dynamic instruction and decides whether or not it may integrate a squashed result. Of course, this must be done for multiple, potentially dependent instructions in parallel. In this section, we present a possible implementation of this logic. We begin with the scalar circuit, then proceed to the superscalar case.

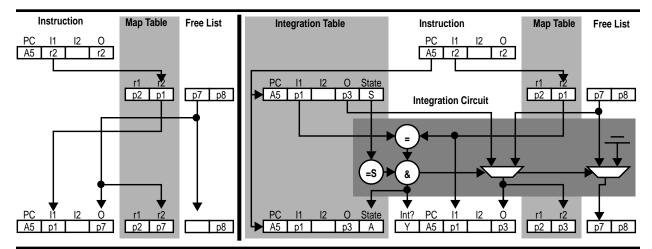

### **3.3.1 Scalar Register Integration**

Shown on the left side of Figure 4, scalar register renaming occurs in two logical steps. First, an instruction's logical inputs are renamed to physical inputs using lookups in the map table. Second, its logical output is allocated a new physical register and this new logical-to-physical mapping is entered into the map table, allowing future instructions that need the value to obtain their inputs from the correct location. We call the two stages *input routing* and *output allocation*, respectively. Integration adds a piece called *output selection* in which the output mapping must be chosen between a newly allocated physical register (no integration) and a physical register obtained from an IT entry (successful integration). The output selection

circuit occurs *logically after* the input routing circuit since the integration test must compare the input physical registers of the sequential instance with those in the IT entry. However, the scalar implementation of integration can be thought of as occurring in one of two ways. In the first, output selection is implemented serially after input routing with the integration table indexed by instruction PC *and* input physical registers. In the second, output selection is split into *IT lookup*, which happens in parallel with input routing, and an *integration test*, which occurs logically after it. In this organization, the IT is indexed by *PC* and the physical register numbers are used as matching tags.

The right side of Figure 4 shows the operation of the PC-indexed integration circuit via the integration of instruction A5 from the example in Figure 1. The figure is sliced both vertically and horizontally. Vertical slices show structures: the integration table (IT), map table, free list and the instruction itself. Horizontal slices show time. The top slice shows the instruction in raw form and the structures before renaming. The bottom slice shows the renamed instruction and the updated structures. The output selection function selects between the physical register from the IT (p3) and a newly allocated one from the free list (p7). The function is implemented by comparing the corresponding input physical registers from the IT entry and the map table (both are p1) and checking that the candidate physical register is in the Squashed state. Successful integration has five effects: 1) the current instruction is marked as integrating, 2) the output of the integrating instruction is set to the physical register entry from the IT, 3) the same physical register is set as the current mapping in the map table, 4) the corresponding IT entry transitions to the Active state, and 5) the newly allocated but unused physical register is returned to the free list.

#### 3.3.2 Superscalar Register Integration

The merits of each implementation are open to debate in the scalar realm, but in a super-scalar environment only the second is viable. While the first scheme interleaves and serializes the input routing and output selection decisions that must be made for each instruction, the PC indexed scheme permits a parallel prefix implementation similar to the one used to "superscalarize" conventional register renaming. Let us review conventional superscalar renaming. Superscalar renaming is more complex than scalar renaming because its input routing decisions must reflect intra-group dependences. In superscalar renaming, *dependence-check logic* acts in parallel with output allocation. This logic compares the logical input of each instruction in the group with the logical output of each previous in-group instruction; a match overrides the initial input routing retrieved from the map table and routes the input to the appropriate newly allocated physical

**FIGURE 4. Scalar Integration Circuit.** On the left is a scalar integration-less, register renaming circuit. On the right is a scalar renaming circuit augmented with register integration. We use the organization in which the IT and map table are accessed in parallel. An extension of this circuit implements superscalar integration. The diagram traces the IT, map table and free list, as well as the instruction itself through the two logical steps of integration-enabled register renaming. At the top of the figure, the instruction shown is raw and the structures are as they appear before the instruction is renamed. At the bottom, the instruction is renamed and the structures reflect that fact. The integrating instruction is A5 from Figure 1.

register. For example, in a group of four two-input, one-output instructions each of the second instruction's inputs has to be compared with the first instruction's output, each of the third instruction's inputs has to be compared with the outputs of the first two instructions and each of the fourth instruction's inputs has to be compared with the outputs of the first three instructions. The total number of comparisons for this case is 12. In general, the number of logical register comparisons required to implement the dependence cross-check is I \* N(N-1)/2, with I the number of inputs per instruction and N, the superscalar width. This number grows as  $N^2$ . The depth of the circuit is linear with N.

In addition to the conventional dependence-check circuit that compares logical registers, integration requires that we implement output selection and any corrections it might imply for input routing for subsequent instructions. Recall, for the scalar integration test we compared each IT entry input with the corresponding register retrieved from the map table. In the superscalar case, we must also compare it to the physical register outputs for all integration candidates of *at most one* prior instruction in the group, the instruction (if it exists) that writes the corresponding logical register. The logical-register dependencecheck logic lets us know the identity (in-group position) of this instruction in advance. Note, there is no need to compare the candidate input with the newly allocated physical registers corresponding to this prior instruction: the situation in which an integrating instruction depends on an older in-group non-integrating instruction is impossible. The priority-encoding depth of the output selection circuit is N. However, the number of physical register comparisons in the circuit grows with both N, superscalar width, and M, the number of possible IT matches or the associativity of the IT. The precise formula is I \* M \* (1 + M \* (N + M))1)). The growth of the function is  $INM^2$ . For instance, a four-wide machine with a direct-mapped IT requires 8 physical register comparisons to implement integration, the same processor with a 2-way IT needs 28 comparisons, while an 8-wide processor with a 4-way IT requires 232 comparisons! Although the complexity of the circuit discourages high-associativity IT implementations, it is actually less complex than we originally thought. In our initial work [19], we did not see the potential for using the logical dependence-check logic to limit the number of physical register comparisons. Believing that each physical register input of each IT entry had to be compared to physical register outputs of the IT entries of all previous in-group instructions, we reported the complexity of the circuit as  $IN^2M^2$ .

We should mention here that it may be possible to reduce the complexity of the integration (output-selection) circuit using different IT organizations. For instance, the IT could internally perform the intra-group dependence checks and store groups of dependent instructions in a kind of "trace" that can be integrated using *INM* comparisons. The obvious problem with this approach is that of choosing the appropriate instruction grouping. Currently, we do not know of any such optimized organizations in particular.

### **3.3.3** Pipelining Register Integration

Although complex, the implementation of the integration circuit is unlikely to slow down the conventional register renaming circuit to the point where it needs to be superpipelined. The reason for this is that although register renaming and integration are semantically *atomic*—a group of instructions can only be renamed and integrated once renaming and integration of the previous instruction group has completed—this is not exactly the case. The atomic portions of both renaming and integration are actually quite small. Many of the component tasks are specific to an instruction group and can be moved up in the pipeline without introducing hazards.

We first consider the implementation of the conventional superscalar renaming circuit. A conventional renaming circuit logically completes six tasks: it 1) reads map table entries, 2) acquires free registers from the free list, 3) computes intra-group dependences, 4) uses the intra-group dependence information to route instruction inputs to the right physical registers, 5) updates the map table, and 6) returns any unused registers to the free list. This is a lot of work and, in addition, it may appear that all of these tasks are interdependent and must be completed before the next group of instructions can be renamed. However, this is not so. Only tasks 1, 4, and 5 must be atomic and, furthermore, tasks 4 and 5 can be performed in parallel. Tasks 2, 3 and 6 are independent of the renaming of prior and future instruction groups and can be computed in earlier pipeline stages or delayed until subsequent stages. For instance, the computation of intra-

group dependences requires only the logical register names of instructions within the group. This information can be computed earlier in the pipeline and transmitted to the critical register renaming stage.

Register integration has a similar character and its components permit a similar organization. We have already seen that the intra-group architectural register dependence-check logic can be moved up in the pipeline. It is also the case that the intra-group *physical-register* dependence-check—the  $INM^2$  physical register comparisons that implement superscalar integration—can be moved up. Now, no integration decision can be finalized until the current physical register mappings are retrieved from the map table. The final integration decisions which require the current mappings from the map table must be performed during the critical stage. However, these can simply aggregate and gate the previously made intra-group decisions using a single layer of AND/OR logic.

The observation that permits the physical-register cross check to be moved away from the critical singlecycle renaming path is that a group of instructions can read its corresponding IT entries before the instructions in the immediately preceding group have finished writing their entries into the IT. The only impact of this dissociation is that instructions in a group lose the ability to integrate the results of instructions from the immediately older group (or the two immediately older groups if IT reading is moved two stages ahead of the last renaming stage). In general, the implementation of register integration easily admits simplifications and omissions of this kind. After all, integration is a performance optimization and failure to integrate a result does not constitute an incorrect execution, only a lost opportunity for performance improvement. However, this particular optimization does not result in even a single lost integration opportunity. Recall, in order to be integration-eligible, a physical register must belong to an instruction that has completed execution and subsequently been squashed. Given the nature of the pipeline, it is impossible for an instruction to complete execution in the cycle immediately after being renamed. In general, a minimum of J cycles must pass between renaming and completion. The implication is that instructions that have been renamed within the previous J cycles are integration-*ineligible* anyway, so it does not matter that the current group of instructions cannot see their IT entries. Depending on the value of J and the degree to which register integration is pipelined, it may be possible to implement IT entry creation after renaming and integration.

We envision register integration being implemented in four stages. In the first stage, the IT is read using the instruction PCs and the intra-group architectural-register dependence check is performed. In the second stage, the IT entries and group dependence information are used as inputs to the intra-group physical-register dependence check circuit which makes the superscalar integration decisions. The third stage performs conventional register renaming and per-instruction scalar integration—the physical register inputs of each IT entry are compared to the physical registers obtained via map table lookups—and combines those results with the results of the superscalar integration circuit. This third and final stage also includes the manipulation of the register state vector/free list. The state vector is read and its results are incorporated into the integration decisions, which are then implemented as state transitions. The output of the third stage is a group of renamed instructions each with an integrating bit, an integration-updated register map table, an updated state vector. In the fourth stage, the integrating bit gates the creation of IT entries and the allocation of execution resources on a per-instruction basis.

### **3.4 Integration Verifier**

Simplifying the register integration circuit and adopting a state-based register management scheme are important differences from our initial integration proposal [19]. However, the most significant change is in the implementation of the verifier. There are two ways to ensure that mis-integrating loads do not retire. Our initial approach was to avoid mis-integrations in the first place by keeping IT loads coherent with program stores. We proposed storing data addresses (and potentially values) in IT entries and using associative matching with in-flight store addresses to remove the appropriate loads from integration consideration. We now believe that this approach is not entirely practical. It requires a considerable amount of matching logic and data paths between the IT and the load and store queues. At the same time, it cannot detect mis-integrations that result from the *absence* of a store along the architectural execution path (there is no store to trigger the snoop), requiring us to implement a backup mechanism for this case. Due to these drawbacks,

we have changed tack and now advocate detecting and correcting mis-integrations rather than trying to avoid them. Ironically, even in this implementation, many mis-integrations can be avoided using a mechanism similar to a load-speculation (i.e., memory disambiguation) predictor [4, 14, 15, 25].

### 3.4.1 In-Order Pre-Retirement Re-Execution

The detection/correction approach is realized by *re-executing* integrating loads and treating a change in the output value as a conventional load mis-speculation. Re-execution enables the use of a simple IT that communicates only with the register renaming stage, while uniformly and unequivocally detecting all mis-integrations. Of course, the problem with re-execution is that it consumes execution bandwidth and core resources. We can rationalize away this "problem" by considering that, were integration not implemented, these resources would have been consumed anyway. However, this justification is unnecessary. The kind of re-execution we propose is not re-execution by the out-of-order core, but a much cheaper form—*in-order pre-retirement re-execution*.

In-order pre-retirement re-execution is a powerful and general technique for simplifying the implementation of microarchitectural mechanisms by relieving them from having to handle difficult but rare corner cases correctly. With re-execution acting as a "safety net", these mechanisms can be implemented more simply and efficiently, potentially resulting in higher overall performance. Register integration fits this profile perfectly. A holistic application of this philosophy is the Dynamic Verification Architecture (DIVA) [1, 2], in which all instructions are re-executed. DIVA's authors make an additional contribution with the observation that, with tentative inputs and outputs supplied by the main execution engine, the re-execution of dependent instructions—and even different stages of the same instruction—can be performed in parallel, driving the performance cost of re-execution to near zero. DIVA is a compelling technique with many applications, making it a strong candidate for implementation in future microprocessors. If that is indeed the case, then our re-execution mechanism is given to us and we need not implement one specifically to support integration. However, it should be noted that register integration does not require a full bandwidth DIVA implementation as only integrating instructions, which typically account for less than 15% of the dynamic retirement stream, must be re-executed.

Earlier, we mentioned that some register management tasks may be turned into verification tasks. One such task is the cascaded freeing of *stale* Squashed registers. When a Squashed register is freed, all dependent Squashed registers technically become un-integrable. A dependent Squashed register that is not freed is stale. If, by chance, the freed register is remapped to the *same* logical register by an unrelated instruction, the stale IT entry creates the false impression the dependent instruction result is valid. We can implement incremental cascaded freeing within the context of our state transition regime. Doing so means that only load mis-integrations are possible (stale entry mis-integrations are impossible) and hence that only integrating loads must be re-executed. We have found that load re-execution can be piggy-backed onto the store retirement ports with almost no performance loss. However, an explicit implementation of cascaded invalidation requires an additional state and some associative matching capability in the IT. Consequently, we omit this functionality from the register state machine, and allow stale-entry mis-integrations to be caught by re-execution. This choice requires a DIVA implementation. Our simulations model a DIVA re-execution pipeline stage that has 25% the execution bandwidth of the out-of-order core. Since integrating instructions comprise about 15% of the retirement stream, this is sufficient to avoid re-execution stalls

### 3.4.2 Avoiding Likely Mis-Integrations

Retirement-time re-execution makes mis-integration detection perfectly accurate—all mis-integrations are caught and no false mis-integrations are signaled—as well as cheap. However, mis-integration recovery is still expensive as it requires squashing and re-fetching the mis-integrating instruction and all subsequent instructions. From a performance standpoint, a mis-integration is an artificially introduced load or branch mis-speculation. Ideally, we would like to avoid mis-integrations in the first place. Fortunately, there is an easy way of doing this that does not involve snooping the IT.

Load mis-integrations are stable and, as a result, predictable. Load mis-integrations result from the presence or absence of different communicating stores—stores that write to the address the load will ultimately read-along different paths to a load. Store-load communication is a function of program structure; it exists specifically to implement some programmer or compiler idiom. Since program structure is fixed (ignoring self-modifying code), store-load communication patterns are fixed and can be predicted with high accuracy. Previous work has established the predictability of store-load communication empirically and exploited it to create predictors for avoiding store-load mis-communication [4, 14, 15, 25]. Store-load mis-communication-also called memory-ordering violation or load mis-speculation-is predictable because it is the product of two fixed entities: 1) program structure and 2) the scheduling policy. The mechanism for avoiding likely load mis-integrations is motivated by, and is structurally very similar to, mechanisms for avoiding load mis-speculations. Load mis-integration is a product of three stable factors: 1) the presence (or absence) of a communicating store along one path to the load, 2) the complementary absence (or presence) of the same store along another path to the load, and to a lesser degree 3) the inability of the branch predictor to predict the correct path. The stability of these factors combine to create a fourth stable and, hence, predictable phenomenon: if an instance of a particular static load results in a mis-integration, then future instances of that load will also (with high probability) result in mis-integration.

We exploit this predictability by augmenting the integration circuit with a small PC-indexed cache called *the load integration suppression predictor (LISP)*. Each LISP entry is a saturating up-down counter. The LISP is accessed in the early stages of the register integration pipeline and updated at retirement by the reexecution engine. The detection of a mis-integration creates an LISP entry if none exists and increments its counter. A successful re-execution (no mis-integration) decrements the counter of an existing entry. The benefit of a successful integration can be weighed against the cost of a mis-integration by the choice of increment, decrement, and suppression threshold values. Empirically, we have found that incorporating branch (path) history into the LISP indexing function improves LISP accuracy appreciably. This is intuitive since the presence or absence of the mis-integration causing store is entirely path dependent. The LISP is effective at suppressing the more common load mis-integrations. It does not capture mis-integrations due to stale IT entries, as these are only very loosely correlated with program structure.

### 3.4.3 Interactions with other Physical Register Disciplines

Squash reuse has some non-trivial interactions with other mis-speculation recovery disciplines. First among these is its interplay with *higher-order integrations*. The possibility and presence of mis-integration creates a squash reuse feedback loop. The integration of squashed instructions raises the possibility of mis-integration, which induces a squash whose instructions can be reused. We call instructions that integrate results squashed due to a control- or data- mis-speculation *primary integrations*. Higher-order integrations are integrations that integrate results squashed due to mis-integrations. In a strange sense, the presence of integration reduces the cost of mis-integration (via the reuse of mis-integration-squashed instructions) while increasing the frequency of mis-integration (via higher order mis-integrations).

Higher-order integrations must be handled carefully. In general, any results squashed due to *data mis-spec-ulations* such as mis-integrations, load mis-speculations (memory-ordering violations) [4, 14, 15, 25], or value mis-speculations [12] must be handled differently than those squashed due to control mis-speculation. Instructions squashed as a result of a control mis-speculation are correct from a data standpoint and their results may be integrated without fear (modulo load mis-integration). Physical registers squashed as a result of a data mis-speculation may not be correct from a data standpoint—they may depend on the mis-speculated instruction—and the likelihood that their integration will result in a mis-integration is high. If caution is not exercised, we could run into an infinite loop where the same mis-integrated instruction is repeatedly mis-integrated, squashed, and mis-integrated again. Obviously, we must avoid this scenario.

One broad solution to this problem is to not perform the Active-to-Squashed transition on recovery from a data mis-speculation. However, this solution is too harsh since it prevents the correctly executed instructions that were lost during recovery from being salvaged. An effective trick is to gate the Active-to-Squashed transition *only* for the data mis-speculated instruction itself, which is forced to transition back to

the Free state. Doing this effectively "detaches" all dependent instructions from possible integration, while leaving all independent instructions intact.

A second interesting interaction exists between integration and another technique for salvaging work lost to a data mis-speculation: *selective squashing* [7, 12, 16, 17]. In selective squashing, instructions are kept in reservation stations until retirement allowing them to simply re-issue as data mis-speculations are resolved. If selective squashing *is* implemented, integration is not "activated" during data mis-speculations since the instructions are not squashed and re-fetched. Integration, on the other hand, still handles control mis-speculation squashes which, quite conveniently, cannot be handled by selective squashing. Integration and selective squashing complement each other. However, we do not explore their interaction experimentally; our simulations model full squashing for all data mis-speculations.

### 3.5 Building a Balanced Register Integration System

Earlier we mentioned the problem of saddling the IT with the dual roles of physical register management and integration brokerage. Fortunately, our choice to create IT entries for all instructions during register renaming forces us to confront this problem, while our use of explicit register states provides the solution. These two components allow us to create a balanced, flexible register integration system that can produce high integration rates with a low integration circuit complexity and no direct adverse interactions with active instructions.

Although IT entries are created for active instructions during renaming, we cannot *require* every active instruction to have an IT entry. Recall, the IT is indexed by PC to facilitate the integration process itself. Forcing correspondence between IT entries and active instructions would create the undesirable situation in which IT set-conflicts stall register renaming. Instead, we exploit our explicit register state scheme to enforce *no* invariant relationships between IT entries and active instructions and, in general, between IT entries and physical registers. In other words, because physical register state is represented explicitly, presence or absence in the IT is not required to deduce this state. A physical register need not be associated with an IT entry and vice versa.

This dissociation not only dissolves the harmful interactions between the IT and active instructions, it also allows the IT and physical register file to be sized independently to maximize integration opportunity while minimizing integration circuit complexity. The size of the physical register file determines the number of integration-eligible Squashed physical registers that can be "in circulation" at any time. Empirically, we have found that for our configuration—which, admittedly, has a large 256-entry reorder buffer—giving the processor the minimal number of physical registers required to store the values for all architectural and speculative (in-flight) values provides the best performance. This may seem completely counter-intuitive as, under this configuration, a full reorder buffer wipes out all squashed results. However, the bulk of successful integration takes place soon after a squash when the reorder buffer is likely to be quite empty. In addition, occasionally flushing all squashed results is actually a desired behavior as it eliminates stale entries that could otherwise lead to mis-integrations.

While technically the IT needs only as many entries as there are physical registers, it is often advantageous to build a larger IT. The reason for this is that reasonable management of a minimally-sized IT may only be performed if the IT is fully associative. Since the IT is indexed by PC and requires *N* read and write ports where *N* is the renaming width of the machine and furthermore since IT associativity may be related (although not necessarily) to integration circuit complexity, a fully associative implementation is impractical. However, while a minimally-sized low-associativity IT (we imagine 4 to be the maximum practical associativity) can be engineered, it will have many PC conflicts that will substantially reduce the number of successful integrations. To compensate for this, we can use a large IT that will disperse PC collisions among many sets and effectively limit conflicts to multiple instances of the same instruction. We will quantify the performance impact of this organization in Section 4.3.1.

## 4 Performance Evaluation

We evaluate the potential performance impact of integration using cycle-level simulation. We present a full sets of results for one specific design meant to represent a potential next-generation microprocessor. We then look at three parameters in the register integration-based squash-reuse design space: IT associativity, IT size, and the mis-integration suppression mechanism. Finally, we discuss the impact of selected base microarchitecture parameters on the applicability and efficiency of register integration.

### 4.1 Experimental Framework

We evaluate integration using the SPEC2000 integer benchmark suite. The programs are compiled for the Alpha EV6 architecture by the Digital UNIX V4 cc compiler with optimizations -O3 -fast. We use the training data sets for reporting performance for all benchmarks. The programs are simulated to completion using 10% cyclic sampling with a granularity of 100 million instructions per sample. Our experiments with unsampled runs [18] show that using cyclic sampling to compute speedups results in very small errors, typically less than 10% of the computed speedup (or slowdown) itself.

Our simulation environment is built on top of the SimpleScalar 3.0 toolkit. The cycle-level simulator models a superscalar, out-of-order processor with nominal stages fetch, decode, register rename and dispatch, schedule and register read, execute, writeback, re-execute/verify and commit and a parametrizable number of pipeline stages in each logical stage. We model a memory system with non-blocking caches, finite write-buffers and MSHRs, and cycle-accurate bus utilization. Table 1 details the simulation parameters.

Since squash reuse feeds on results of instructions that were squashed due to a mis-speculation, we simulate a processor that speculates aggressively. The processor we model can fetch, dispatch, issue and retire 8 instructions per cycle. Each cycle, instructions can be fetched from multiple cache lines with up to one internal taken branch. The processor can speculate past an unlimited number of branches. The processor has large instruction buffers. Up to 256 instructions may be simultaneously in-flight in the execution core, with up to 128 loads and 64 stores. There is a centralized pool of 120 reservation stations, so at any point only 120 of the 256 in-flight instructions may be un-issued. Of the 8 instructions that can be executed every cycle, two may be loads and two more may be stores. The out-of-order scheduling logic speculates loads aggressively, issuing them in the presence of older stores with unavailable addresses. A mis-speculation

| Front-End               | 2K-entry combined 6-bit history gshare and bimodal predictor with 2-bit saturating counters. 1K entry, 4-way associative BTB, 16 entry return-address-stack. 3-cycle fetch. 8-entry instruction buffer. Up to 8 instructions from two cache blocks fetched per cycle. A maximum of one taken branch per cycle. 8-wide single-cycle decode. Recovery from BTB misses for direct, unconditional jumps triggered at decode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Execution<br>Engine     | 8-wide superscalar out-of-order speculative issue with a maximum of 256 instructions or 128 loads or 64 stores in-flight. 2-cycle register renaming and dispatch stage renames to 512 physical registers. 120 reservation stations. 4-cycle schedule/register read. A maximum of 8 instructions scheduled every cycle, with up to 4 integer ALU operations, 2 loads, 2 stores, 2 FP operations and 1 branch. Memory and control instructions have the highest scheduling priority. Priority within a group is determined by age. Loads speculatively issue in the presence of older stores with unknown addresses. The load and subsequent instructions are squashed and refetched on an early issue. Recovery from all forms of mis-speculation is monolithic. Address generation takes 1 cycle and store-to-load forwarding via the store queue takes 2 cycles. The processor has 4 1-cycle integer ALUs, 1 1-cycle branch unit, 1 3-cycle fully-pipelined FP adder, 1 4-cycle fully-pipelined integer/FP multiplier, and 1 20-cycle, non-pipelined integer/FP divider. |

| Memory<br>System        | 32KB, 32B lines, 2-way associative, 1-cycle access L1 instruction cache. 32KB, 32B lines, 2-way associa-<br>tive, 2-cycle access, L1 data cache. A maximum of 16 outstanding load misses. 16-entry store buffer. 16-entry<br>ITLB, 32-entry DTLB with 30-cycle hardware miss handling. 1MB, 64B line, 4-way associative, 12-cycle<br>access L2 cache. 70-cycle memory latency. 32B bus to L2 cache clocked at processor frequency. 16B bus to<br>memory clocked at 1/3 processor frequency. Cycle-level bus utilization modeled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Register<br>Integration | 1K entry, 4-way set associative integration table. A direct-mapped, 256-entry load integration suppression predictor (LISP) indexed by XORing the PC with 4 bits of branch history. Each LISP entry is a 4-up, 1-down saturating counter with a threshold of 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Re-Execution<br>Engine  | Integrating instructions are re-executed prior to retirement. The processor can re-execute up to 2 instructions per cycle, with a maximum of 1 load or store re-executed per cycle. Mis-integration detection triggers a flush that includes the offending instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

TABLE 1. Simulated Processor Configuration.

causes the load and all downstream instructions to be monolithically squashed and refetched. We model an aggressive dependence-speculation mechanism [4, 14, 15, 25] that reduces the incidence of conventional load mis-speculations nearly to zero.

We also model an aggressive but non-ideal register integration configuration. Our mechanism uses a 1Kentry 2-way set-associative integration table (IT). The processor is not equipped with additional physical registers to explicitly store squashed results. At any time, squashed results can only be stored in those registers that are not allocated to in-flight instructions or architectural values. The load integration suppression predictor (LISP) is direct-mapped with 256 entries. To index the LISP, we XOR the load PC with 4 branch history bits. For verification purposes, all integrating instructions are re-executed. Our simulated processor can re-execute up to two integrating instructions every cycle with a maximum of one load or store. On misintegration detection, the entire pipeline is flushed, including the mis-integrating instruction itself. Although its proper value is available, we do not provide additional paths to send re-executed results back to the main execution core. All recovery is modeled as monolithic and occurring in one cycle.

### 4.2 Base Configuration Results

Table 2 on the next, which is split into two for readability, shows the performance impact of integration using the configuration described above. Data is presented in four parts. The first two characterize the performance of the base and integration-enhanced system in terms of instructions fetched and executed, branch mispredictions, branch misprediction resolution latency, and instructions retired per cycle (IPC). Comparing these groups of numbers pair-wise gives an idea of the overall effect of integration on speculative (mis-speculative) processor activity. The next two parts measure the activity and effectiveness of integration using more direct metrics.

In the first bold portion at the bottom of the table, we report the absolute count of instructions squashed. This count contains only instructions squashed after having completed execution, i.e., integration candidates. We also show the number of integrating instructions and integrating mispredicted branches (these are the ones whose mispredictions were immediately resolved), and the number of mis-integrations. Integrating instruction counts do include higher-order integrations, integrations of results that were squashed due to a mis-integration. However, integration counts are measured during instruction retirement to avoid counting integrating instructions that were subsequently squashed, and double-counting integrating instructions that were subsequently squashed and re-integrated. Note, the counts of mis-integrations and integrating mispredicted branches are reported in *thousands* (K); other counts are reported in *millions* (M).

In the second bold portion, we compute the characteristic metrics of integration and its impact on performance. The *squash rate* is the number of integration candidates as a percentage of the total number of instructions committed; it is a measure of the amount of work available for squash reuse to exploit. The *salvage rate* is number of integrating instructions as a percentage of integration candidates and measures the rate at which integration candidates are harvested. The *contribution rate* is the number of integrating instructions as a percentage of the total number of instructions committed; it is the amount of work integration contributes to the architectural execution of the program. The contribution rate is the product of the squash and salvage rates. The final three metrics measure the percentage reduction in instructions fetched, instructions executed, and total execution time due to integration.

### 4.2.1 Register Integration and Program Structure